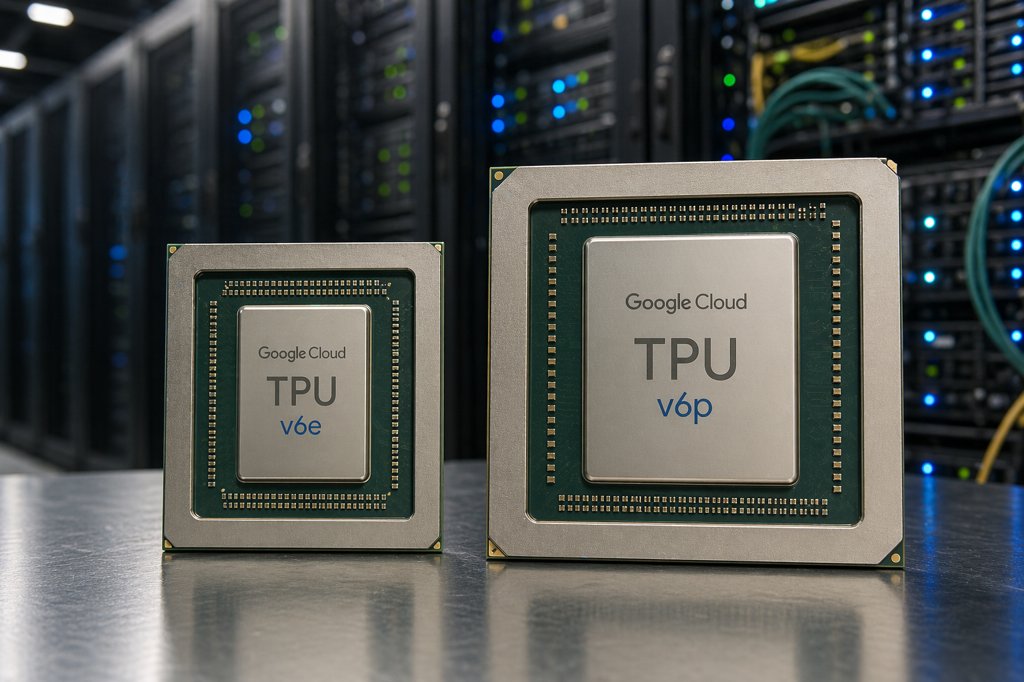

Google ha rilasciato simultaneamente la sesta generazione di Tensor Processing Unit (TPU), declinata in due varianti distinte: la TPU v6p e la TPU v6e. Questa decisione strategica di non produrre un singolo chip “universale” riflette una profonda comprensione della diversificazione dei carichi di lavoro legati all’intelligenza artificiale, segnando il passaggio da un’era di forza bruta computazionale a una di efficienza specializzata per specifici compiti di addestramento e inferenza.

La ragione tecnica principale che ha spinto Google a sviluppare due unità distinte risiede nella necessità di bilanciare prestazioni massime ed efficienza economica. La TPU v6p (dove “p” sta per performance) è stata progettata come il fiore all’occhiello per l’addestramento dei modelli più grandi e complessi, come quelli della famiglia Gemini. Questo chip è ottimizzato per carichi di lavoro che richiedono una larghezza di banda di memoria elevatissima e una comunicazione ultra-rapida tra i nodi, fondamentale per sincronizzare i parametri di modelli che superano il trilione di parametri. La v6p utilizza tecnologie di raffreddamento a liquido avanzate e interconnessioni ottiche proprietarie per gestire cluster di dimensioni enormi, garantendo che il collo di bottiglia non sia la potenza del singolo chip, ma la capacità del sistema di scalare linearmente.

La TPU v6e (dove “e” sta per efficiency) è stata concepita per democratizzare l’accesso all’IA di alta qualità, focalizzandosi sull’inferenza e sull’addestramento di modelli di medie dimensioni. La v6e è ottimizzata per massimizzare il rapporto tra prestazioni e prezzo per watt. Dal punto di vista descrittivo, questa unità permette di eseguire carichi di lavoro di intelligenza artificiale generativa con una latenza estremamente ridotta, rendendola ideale per applicazioni commerciali su larga scala dove il costo operativo per query è il parametro critico. Questa distinzione permette a Google di offrire alle aziende un’infrastruttura flessibile: utilizzare la v6p per la fase intensiva di sviluppo del modello e migrare sulla v6e per la fase di distribuzione globale, ottimizzando i costi senza sacrificare l’accuratezza.

Questo segnale inviato al mercato dell’IA indica chiaramente che il futuro non appartiene più a un hardware generico, ma a un ecosistema di acceleratori progettati per fasi specifiche del ciclo di vita del modello. L’architettura delle TPU v6 integra inoltre miglioramenti significativi nella gestione dei carichi di lavoro sparsi (sparse workloads), essenziali per le architetture Mixture-of-Experts (MoE) che dominano l’attuale panorama tecnologico. Producendo due TPU diverse, Google non solo risponde alle esigenze di scala dei propri servizi, ma stabilisce un nuovo standard industriale dove l’ottimizzazione del silicio è guidata dalla diversità degli algoritmi, permettendo un’allocazione delle risorse computazionali molto più granulare e sostenibile rispetto al passato.