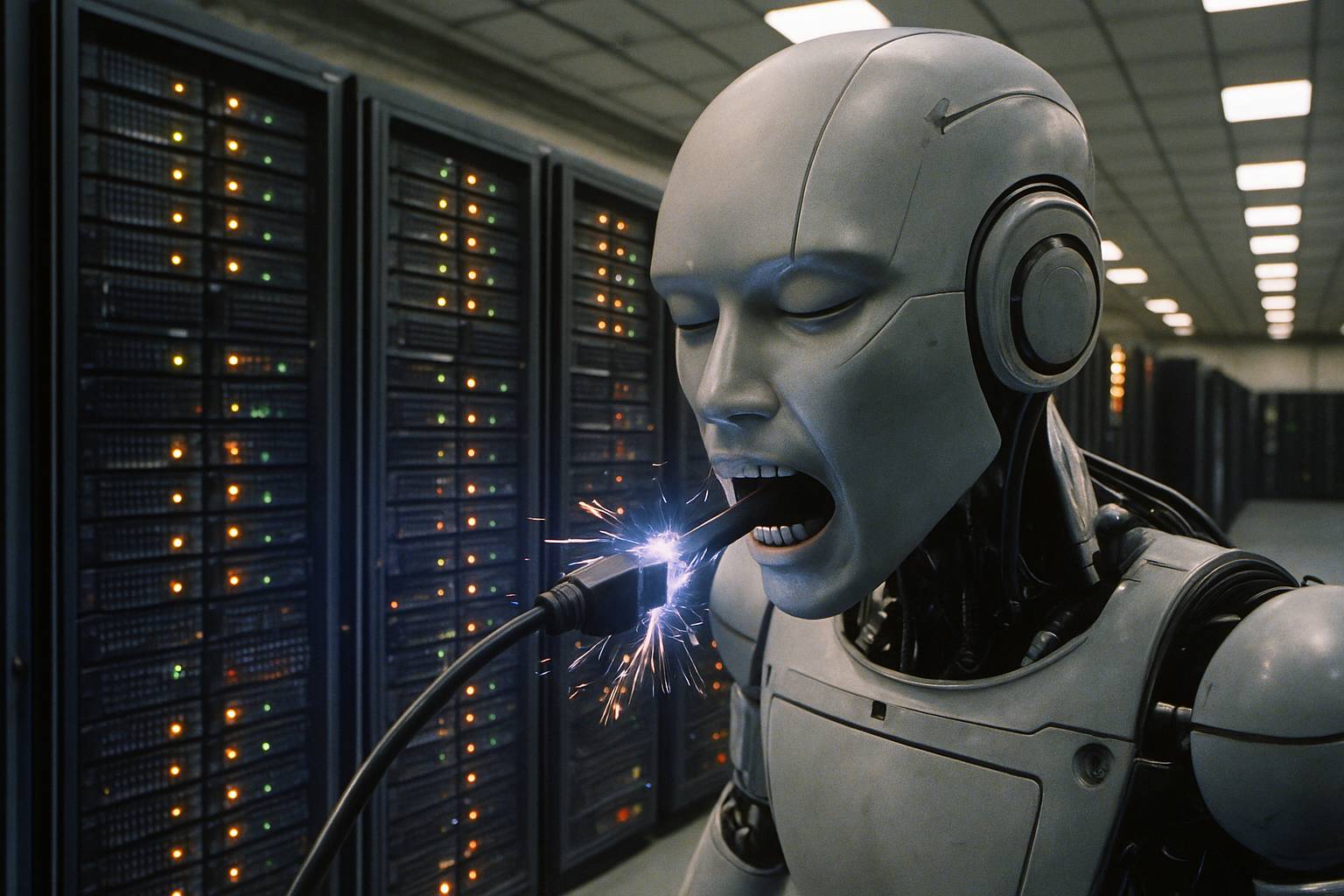

L’intelligenza artificiale mangia elettricità. Questa immagine, forse fin troppo cruda, non è lontana dalla realtà: nelle enormi sale server che alimentano i modelli di linguaggio, le reti neurali e le applicazioni “in tempo reale”, il fabbisogno energetico è esploso negli ultimi anni. E la sfida non è solo quella di produrre più energia — è quella, ancora più sottile e critica, di portarla fino al silicio senza disperderla. In altre parole: non basta avere un’auto potente, serve un motore che riceva la benzina senza perdite. Ed è qui che entrano in gioco i regolatori di tensione integrati, noti come IVR (Integrated Voltage Regulators), che stanno riscrivendo le regole dell’architettura dei chip per l’era dell’IA.

Per capire l’importanza di questa innovazione, occorre partire dal concetto di “ultimo tratto” — l’ultimo segmento del percorso dell’energia che va dalla rete elettrica fino al cuore del chip. Tradizionalmente, l’energia viaggia in più fasi: da corrente alternata ad alta tensione si passa a tensioni più basse, fino ad arrivare a correnti continue (DC) a bassissima tensione, compatibili con i transistor. Le conversioni avvengono generalmente lontano dal chip, su componenti discreti montati sulla scheda madre: controller, stadi di potenza, induttori avvolti finemente su filo, e così via. È un sistema collaudato. Eppure, nell’era in cui i carichi variantissimi, improvvisi e intensi dell’IA fanno oscillare i consumi, questa architettura mostra i suoi limiti.

Uno dei problemi principali è la dissipazione di energia. Man mano che l’elettricità percorre il circuito, parte della potenza si perde per effetto Joule (la famosa “resistenza × corrente al quadrato”), trasformandosi in calore. Più lungo è il tragitto, più energia si disperde. In ambienti dove ogni watt conta, queste perdite diventano insostenibili. Inoltre, i regolatori discretamente posizionati non sono sempre abbastanza rapidi da rispondere alle variazioni improvvise richieste dal processore, noti come “transient load”: quando il carico passa da inattivo a piena attività, serve una risposta immediata. Se il regolatore non tiene il passo, si genera un fenomeno chiamato “voltage droop”, una caduta temporanea di tensione che può compromettere il funzionamento del chip. Per evitarlo, i progettisti devono sovradimensionare la tensione operativa di base, con un conseguente spreco energetico. Infine, questi moduli occupano spazio prezioso sulla scheda madre: attorno al processore ogni millimetro vale oro, e liberarlo significa guadagnare capacità per altri componenti, interconnessioni più rapide o design più audaci.

La soluzione che sta emergendo è tanto elegante quanto rivoluzionaria: spostare il regolatore di tensione il più vicino possibile al carico, fino a integrarlo direttamente nel chip o nella sua confezione (package). Grazie ai progressi nella tecnologia magnetica a film sottile, è oggi possibile realizzare induttori estremamente compatti e performanti direttamente sulla superficie del substrato del chip. In questo modo il tragitto dell’energia si riduce drasticamente, da centimetri a micrometri. Il risultato è una forte riduzione delle perdite, una risposta quasi istantanea ai carichi variabili, e la possibilità di gestire domini di potenza diversi all’interno dello stesso chip: ogni nucleo o blocco funzionale riceve solo ciò di cui ha bisogno, nel momento in cui serve, e può spegnersi autonomamente quando è inattivo.

Una conseguenza straordinaria è che il fenomeno del voltage droop diventa quasi inesistente: i regolatori integrati rispondono con latenza nell’ordine dei nanosecondi. Questo permette di abbassare la tensione operative nominale, riducendo ulteriormente il consumo energetico, senza sacrificare la stabilità del sistema. E liberando la scheda madre da componenti ingombranti, si spalancano le porte a configurazioni hardware più dense e sofisticate, in cui chiplet, stacking 3D e soluzioni eterogenee (ossa di calotta con più die di funzione diversa) diventano più praticabili.

Naturalmente, l’ingresso degli IVR non è privo di ostacoli. Integrare nuovi materiali, processi magnetici e componenti non standard all’interno di un ecosistema produttivo di semiconduttori, già così complesso e consolidato, è una sfida enorme. Ogni nuovo passo deve superare la diffidenza dei costruttori, la necessità di garantire affidabilità, compatibilità termica, tolleranza alle vibrazioni, variazioni di temperatura e condizioni operative estreme. Ma la posta in gioco è altissima: se la corsa all’efficienza elettrica è perdente, il costo energetico di mantenere e far crescere infrastrutture di IA potrebbe rallentare o rendere insostenibile la scalata dei modelli sempre più grandi.

Allo stato attuale, il consumo dei data center rappresenta circa il 2 % dell’elettricità mondiale, e le proiezioni indicano che questa quota è destinata a salire con l’espansione delle applicazioni di intelligenza artificiale a livello globale. La potenza disponibile per supportare modelli giganteschi e operazioni in tempo reale rischia di diventare il vero collo di bottiglia dell’innovazione. I regolatori integrati, aziende come Ferric che li sviluppano e le tecnologie abilitanti che li rendono possibili, stanno infatti ridefinendo la frontiera dell’hardware, trasformando un dettaglio di ingegneria in una leva strategica. Non si tratta più solo di aumentare la densità dei transistor o la frequenza operativa: la vera sfida è ripensare da zero come l’energia venga fornita e gestita nei chip di domani.

In definitiva, l’ascesa dei regolatori integrati rappresenta una svolta tecnologica che va ben oltre l’ottimizzazione: è una risposta strutturale alla crescente “sete” di energia dell’IA. Domare la bestia dell’elettricità significa non solo spingere l’hardware oltre i limiti attuali, ma anche ridisegnare l’ecosistema delle architetture di calcolo in chiave sostenibile. E in questa partita, chi vincerà la battaglia dell’efficienza potrà segnare il prossimo grande balzo dell’intelligenza artificiale.