Non capita spesso che il mondo dei semiconduttori venga capovolto. È chiaro che una trasformazione simile si sta verificando quando una sovrabbondanza di start-up affronta la sfida delle reti neurali a bassa potenza.

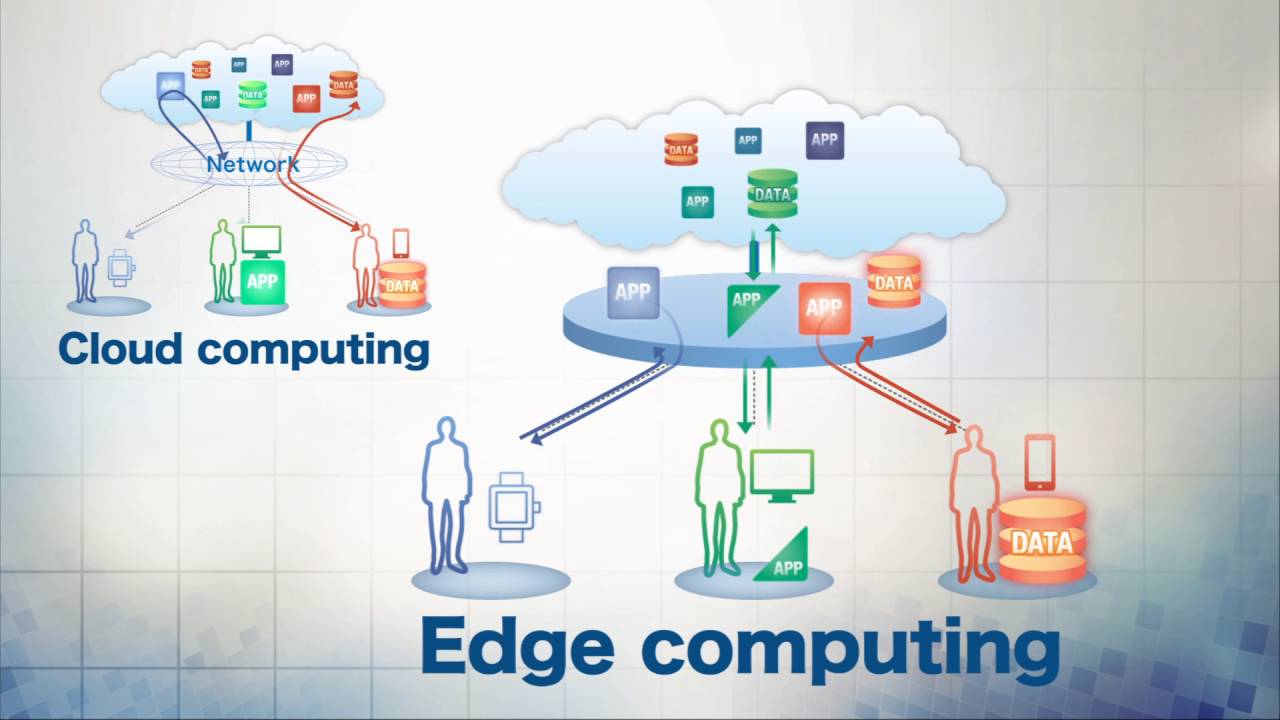

Queste start-up stanno cercando di spostare l’ apprendimento automatico basato su reti neurali dal data center cloud ai sistemi incorporati sul campo, a quello che ora viene chiamato “il bordo”. Far funzionare i chip in questo nuovo mondo richiederà nuovi modi di impostare i neurali, progettare percorsi di memoria e compilare sull’hardware.

Stabilire questa nuova formula sfiderà le teste più brillanti dell’ingegneria elettrica. Ma è iniziata la spinta per l’IA edge. Ha generato una miriade di startup, tra cui Axelera.AI , Deep Vision , EdgeQ , Hailo , Sima.ai e molte altre.

Le opportunità abbondano per le startup di edge AI

A guidare questo, secondo la società di analisi ABI Research, è la necessità di elaborazione dei dati locali, bassa latenza ed evitare chiamate ripetute ai chip AI sul cloud. L’azienda cita anche una migliore privacy dei dati come impulso. È tutto visto come un’apertura per i nuovi arrivati in un mercato di chipset AI edge che ABI stima crescerà fino a $ 28 miliardi nel 2026, per un tasso di crescita annuale composto (CAGR) del 28,4% dal 2021 al 2026.

Questa crescita richiederà progetti che vadano oltre le app AI più avanzate, come quelle che riconoscono le immagini di cani e gatti, create in data center cloud ricchi di energia. Quella ricerca per espandere i casi d’uso dovrebbe mettere in pausa gli ottimisti.

“Fare i chip è una cosa, ma farli funzionare su molti diversi tipi di reti neurali è un’altra. Non siamo ancora arrivati”, ha affermato Marian Verhelst, ricercatrice di circuiti e sistemi presso la Katholieke Universiteit Leuven e l’hub tecnologico Imec in Belgio, nonché membro della TinyML Foundation, che ha parlato con VentureBeat.

“Tuttavia, è un momento davvero fantastico per essere attivi in questo nuovo dominio”, aggiunge Verhelst, che è anche consulente di Axelera.AI, con sede nei Paesi Bassi. La società ha recentemente guadagnato $ 12 milioni in finanziamenti iniziali dal fornitore di infrastrutture di sicurezza Bitfury per perseguire i chip Edge AI.

Cosa conta quando si tratta di progettare questa nuova generazione di chip? I progettisti di chip e i loro clienti devono ora esplorare la questione. In un’intervista, Verhelst ha delineato i punti urgenti come li ha visti:

La forma della rete neurale è importante. Il riutilizzo dei punti dati consente di risparmiare energia nell’elaborazione neurale, ma diversi schemi neurali portano a diversi compromessi di progettazione. Devi decidere quanto flessibile e programmabile dal software vuoi che il tuo sistema sia – e questo influisce sulle prestazioni dell’area di potenza. Ha detto Verhelst: “Quanto puoi utilizzare uno specifico elemento di dati dipende fortemente dalla topologia specifica del tuo livello di rete neurale. Si scopre che non esiste un’unica architettura in grado di [gestire] tutti i tipi di reti neurali in modo efficiente. La questione è se è possibile rendere il controllo del flusso di dati sufficientemente flessibile da poter essere mappato su un’ampia varietà di livelli neurali”.

La gerarchia dei percorsi di memoria è importante. Mantenere il processore alimentato con i dati è l’obiettivo nella progettazione di un percorso di memoria per l’elaborazione neurale. Ha detto Verhelst: “Con la legge di Moore, possiamo mettere molti moltiplicatori su un chip. Questa è la parte facile. La sfida è fornire a tutti loro i dati necessari ad ogni ciclo di clock e per farlo è necessaria una gerarchia di memoria con larghezza di banda sufficiente, in cui i dati vengono riutilizzati a livelli diversi a seconda di quanto spesso sono necessari nuovamente i dati. Questo può davvero avere un impatto sulle prestazioni.”

La mappatura degli algoritmi è importante. La compilazione del codice per l’esecuzione efficiente sull’hardware sottostante è una sorta di eterna ricerca. Tuttavia, sebbene questa sia un’arte quasi padroneggiata per i circuiti integrati convenzionali, è ancora un lavoro in corso per i chip Edge AI. Ha detto Verhelst: “Le catene di compilatori non sono ancora mature. Non esiste un flusso di compilazione standardizzato, sebbene le persone stiano cercando di svilupparlo con iniziative come EVM e Glow. Il problema è che ogni acceleratore ha un aspetto diverso. Le persone devono creare le proprie funzioni del kernel di basso livello per acceleratori specifici. E questo è davvero un lavoro manuale doloroso”.

Queste questioni guidano le decisioni di progettazione in Axelera AI. L’azienda si sta preparando a lanciare sul mercato un chip acceleratore incentrato sull’elaborazione in-memory analogica, reti neurali del trasformatore e architettura del flusso di dati, consumando meno di 10 watt.

“Abbiamo messo insieme l’elaborazione in memoria, che è un nuovo paradigma nella tecnologia, e lo uniamo con un’architettura del flusso di dati , che offre molta flessibilità in un ingombro ridotto, con un consumo energetico ridotto”, ha affermato il cofondatore e CEO di Axelera Fabrizio Del Maffeo, che ha sottolineato che si tratta di un acceleratore in grado di funzionare con un assortimento di CPU “agnostico”.

Del Maffeo cita i sistemi di visione, le città intelligenti, la produzione, i droni e la vendita al dettaglio come obiettivi per gli sforzi di Edge AI.

La competizione per creare una soluzione nell’IA edge è dura, ma imprenditori come Del Maffeo e ingegneri come Verhelst accetteranno con entusiasmo la sfida.

“È un momento molto interessante per hardware, chip, designer e startup”, ha affermato Verhelst. “Per la prima volta in un paio di decenni, l’hardware torna davvero al centro dell’attenzione”.

Senza dubbio, è interessante essere presenti quando nasce una nuova architettura IC.