Intel presenta il suo chip di controllo del calcolo quantistico di seconda generazione

Quando si tratta delle aspettative dei clienti, la pandemia ha cambiato tutto

Scopri come accelerare il servizio clienti, ottimizzare i costi e migliorare il self-service in un mondo incentrato sul digitale.

Intel ha presentato oggi il suo chip di controllo del calcolo quantistico di seconda generazione durante l’evento virtuale Intel Labs. Il chip, nome in codice Horse Ridge II , è un’altra pietra miliare per rendere il calcolo quantistico, uno dei Sacri Graal dell’informatica, più pratico. Il nuovo prototipo si basa sul controller Horse Ridge di prima generazione introdotto nel 2019. Horse Ridge II ha più capacità e livelli di integrazione più elevati per controllare un computer quantistico, che rimane un obiettivo a lungo termine per l’azienda.

All’inizio del progetto, i ricercatori di Intel hanno progettato il System-on-Chip (SOC) scalabile per funzionare a temperature criogeniche, semplificando l’elettronica di controllo e le interconnessioni necessarie per scalare e far funzionare in modo elegante grandi sistemi di calcolo quantistico. La maggior parte dei sistemi informatici quantistici funziona davvero solo a temperature prossime allo zero. Intel sta cercando di cambiare la situazione, ma nel frattempo il chip di controllo elimina la necessità di far passare centinaia di cavi in un case refrigerato che ospita il computer quantistico.

I ricercatori quantistici stanno lavorando solo con un numero limitato di qubit, o bit quantistici, utilizzando sistemi più piccoli e progettati su misura circondati da complessi meccanismi di controllo e interconnessione. L’applicazione dell’informatica quantistica ai problemi del mondo reale si basa innanzitutto sulla capacità di scalare e controllare migliaia di qubit contemporaneamente, con alti livelli di fedeltà.

L’aumento del conteggio dei qubit innesca altri problemi che mettono alla prova la capacità e il funzionamento del sistema quantistico. Uno di questi potenziali impatti è un calo della fedeltà e delle prestazioni dei qubit. Nello sviluppo dell’originale Horse Ridge, Intel ha ottimizzato la tecnologia di multiplexing che consente al sistema di scalare e ridurre gli errori da “sfasamento”, un fenomeno che può verificarsi quando si controllano molti qubit a frequenze diverse, con conseguente crosstalk tra qubit. Gli ingegneri possono sintonizzare varie frequenze sfruttate con Horse Ridge con alti livelli di precisione, consentendo al sistema quantistico di adattarsi e correggere automaticamente lo sfasamento quando si controllano più qubit con la stessa linea di radiofrequenza (RF), migliorando la fedeltà del gate qubit.

Con Horse Ridge II, i ricercatori di Intel hanno aggiunto la capacità di manipolare e leggere gli stati dei qubit e controllare il potenziale di diversi gate necessari per intrecciare più qubit, secondo un discorso di Jim Clarke, direttore dell’hardware quantistico nel gruppo di ricerca sui componenti di Intel.

Perchè importa

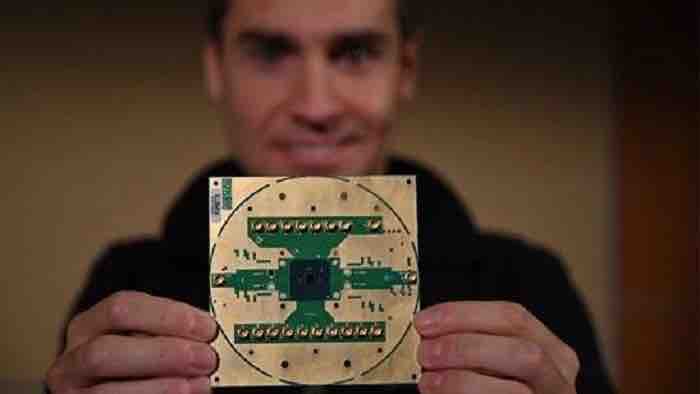

Stefano Pellerano, Principal Engineer presso Intel Labs, detiene Horse Ridge. Il nuovo chip di controllo criogenico accelererà lo sviluppo di sistemi di calcolo quantistico full-stack, segnando una pietra miliare nello sviluppo di un computer quantistico commercialmente valido.

Intel ha affermato che i primi sistemi quantistici odierni utilizzano elettronica a temperatura ambiente con molti cavi coassiali instradati al chip qubit all’interno di un frigorifero a diluizione. Questo è il motivo per cui il chip che vedi nell’immagine è circondato da fili e sistemi di raffreddamento criogenici. Questo approccio non si adatta a un numero elevato di qubit a causa del fattore di forma, del costo, del consumo energetico e del carico termico dell’unità di refrigerazione. Con l’originale Horse Ridge, Intel ha compiuto il primo passo per affrontare questa sfida eliminando la necessità di più rack di apparecchiature e migliaia di cavi che entrano ed escono dal frigorifero per far funzionare la macchina quantistica. Intel ha sostituito questi ingombranti strumenti con un SoC (System-on-Chip) altamente integrato che semplifica la progettazione del sistema e utilizza sofisticate tecniche di elaborazione del segnale per accelerare i tempi di configurazione,

Horse Ridge II si basa sulla capacità del SoC di prima generazione di generare impulsi RF per manipolare lo stato del qubit, noto come qubit drive. Introduce due funzionalità di controllo aggiuntive, aprendo la strada a un’ulteriore integrazione di controlli elettronici esterni nel SoC operante all’interno del frigorifero criogenico.

Ad esempio, una funzionalità chiamata lettura qubit garantisce la possibilità di leggere lo stato corrente del qubit. La lettura è significativa, poiché consente il rilevamento dello stato dei qubit su chip a bassa latenza senza memorizzare grandi quantità di dati, risparmiando così memoria e energia. Intel ha aggiunto un microcontrollore programmabile all’interno del circuito integrato per consentire a Horse Ridge II di offrire livelli più elevati di flessibilità nel modo in cui vengono eseguite le tre funzioni di controllo. Il microcontrollore utilizza tecniche di elaborazione del segnale digitale per eseguire filtri aggiuntivi sugli impulsi, contribuendo a ridurre la diafonia tra i qubit.

Intel ha realizzato Horse Ridge II con un processo di produzione FinFET a basso consumo di 22 nanometri. Funziona a una temperatura di 4 kelvin, o meno 452 gradi Fahrenheit. È piuttosto freddo, solo una frazione sopra lo zero assoluto.

Gli spin qubit al silicio, che sono alla base degli sforzi quantistici di Intel, hanno proprietà che potrebbero consentire loro di funzionare a temperature di 1 kelvin o superiori, il che ridurrebbe significativamente le sfide della refrigerazione del sistema quantistico. Intel descriverà ulteriormente i dettagli tecnici alla Conferenza internazionale sui circuiti a stato solido (ISSCC) nel febbraio 2021.

Nel frattempo, Intel ha anche annunciato progressi nell’integrazione della fotonica con silicio a basso costo e ad alto volume. I progressi rappresentano un progresso fondamentale nel campo delle interconnessioni ottiche, che affrontano le crescenti sfide relative alla scalabilità delle prestazioni di input / output elettrico (I / O) poiché i carichi di lavoro di dati affamati di calcolo travolgono sempre più il traffico di rete nei data center. Intel ha dimostrato i progressi negli elementi costitutivi della tecnologia chiave, inclusa la miniaturizzazione, aprendo la strada a una più stretta integrazione delle tecnologie ottiche e del silicio.

L’industria informatica si sta rapidamente avvicinando ai limiti pratici delle prestazioni di I / O (input-output) elettrico. Poiché la richiesta di larghezza di banda per il calcolo del datacenter continua ad aumentare, l’I / O elettrico non viene ridimensionato per tenere il passo, determinando un “muro di alimentazione I / O” che limita la potenza disponibile per le operazioni di elaborazione. Portando l’I / O ottico direttamente nei server e nei pacchetti di chip, Intel spera di abbattere questa barriera, consentendo ai dati di spostarsi in modo più efficiente.

All’evento Intel Labs, la società ha dimostrato i progressi chiave nei blocchi di costruzione, che includono la generazione di luce, l’amplificazione, il rilevamento, la modulazione, i circuiti di interfaccia CMOS (complementary metal-oxide semiconductor) e l’integrazione dei pacchetti, tutti elementi essenziali per ottenere la fotonica integrata. Un prototipo mostrato all’evento prevedeva uno stretto accoppiamento di fotonica e tecnologie CMOS, che fungeva da prova del concetto della futura piena integrazione della fotonica ottica con il silicio di calcolo del nucleo. Intel ha anche presentato i modulatori micro-ring che sono 1.000 volte più piccoli dei componenti tradizionali. Le grandi dimensioni e il costo dei modulatori al silicio convenzionali sono stati un ostacolo per portare la tecnologia ottica su pacchetti di server, che richiedono l’integrazione di centinaia di questi dispositivi.