IBM riprogetta il mainframe con il nuovo processore Telum

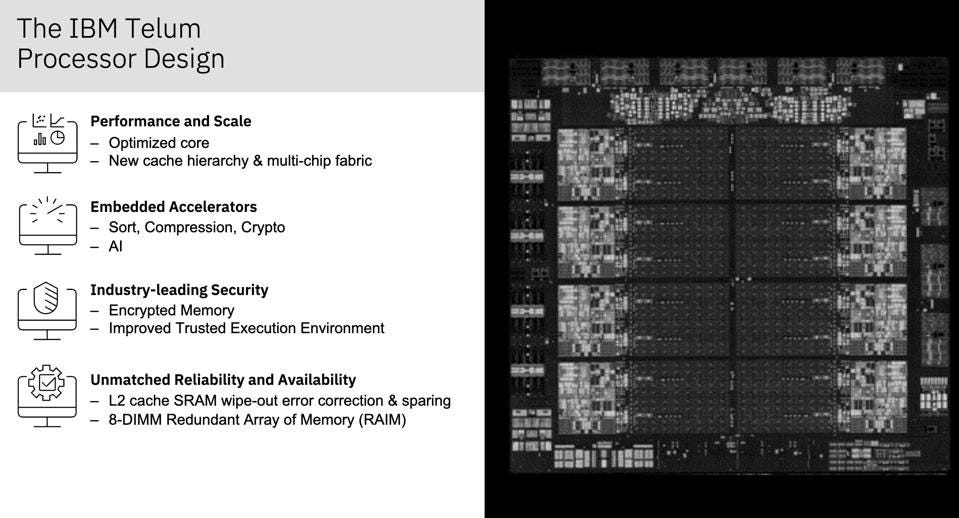

Analogamente a quanto fatto dall’azienda con i nuovi processori Power10 per i sistemi cloud, anche IBM ha iniziato da zero nella progettazione di un nuovo processore per il mainframe IBM Z dell’azienda. IBM Z ha una lunga storia ed è unico in quanto utilizza ancora processori progettati appositamente per la sicurezza, l’affidabilità, la scalabilità e le prestazioni aziendali. Il nuovo processore Telum per la prossima generazione di IBM Z, migliora tutti questi aspetti e aggiunge l’accelerazione integrata, qualcosa che la maggior parte dei sistemi sta realizzando attraverso acceleratori discreti. IBM ha presentato questa mattina il nuovo processore Telum alla conferenza annuale sulla tecnologia Hot Chips.

Una chiave per il design del processore Telum era mettere tutto su un die per prestazioni ed efficienza. Il processore Telum dispone di 8 core CPU, acceleratori del carico di lavoro su chip e 32 MB di quella che IBM chiama cache semi-privata. Ogni modulo chip sarà caratterizzato da due die Telum strettamente accoppiati per un totale di 16 core per socket. Solo per indicare quanto sia diversa questa architettura, il precedente processore z15 presentava dodici core e un chip separato per una cache condivisa. Anche il processore Telum sarà prodotto con il processo Samsung a 7 nm rispetto al processo a 14 nm utilizzato per il processore z15.

Oltre agli stessi core di elaborazione, il cambiamento più significativo riguarda la struttura della cache. Ogni core della CPU ha una cache L1 dedicata e 32 MB di cache L2 “semi-privata” a bassa latenza. Il motivo per cui è “semi-privato” è perché le cache L2 vengono utilizzate insieme per creare un L3 virtuale condiviso da 256 MB tra i core sul chip. Le cache L2 sono collegate tramite un design ring bus bidirezionale per le comunicazioni e in grado di supportare una larghezza di banda di oltre 320 GB/s con una latenza media di appena 12 ns. Le cache L2 vengono utilizzate anche per creare una cache L4 virtuale condivisa tra tutti i chip in un cassetto. Ci sono fino a quattro socket per cassetto e due processori per socket, per un totale di fino a otto chip e 64 core CPU con 2 GB di cache L4 condivisa per cassetto. Questo può quindi essere scalato fino a quattro cassetti nel rack per un massimo di trentadue chip e 256 core CPU.

L’architettura della cache è stata abbinata a miglioramenti nei core e negli acceleratori della CPU. I core della CPU Telum sono un design fuori servizio con SMT2 (Simultaneous Multithreading) che può funzionare a una frequenza di base di 5 GHz o superiore. I core della CPU presentano anche, tra le altre cose, miglioramenti nella previsione delle filiali per grandi dimensioni e carichi di lavoro aziendali diversificati. Il processore Telum offre anche memoria crittografata e miglioramenti all’ambiente di esecuzione affidabile per una maggiore sicurezza e acceleratori on-chip dedicati per l’ordinamento, la compressione, la crittografia e l’intelligenza artificiale (AI) per scalare con il carico di lavoro.

Perché l’accelerazione è così importante?

Una delle dinamiche chiave dell’industria elettronica di oggi è l’informatica accelerata. Tutto, dagli smartphone ai server cloud, utilizza blocchi di elaborazione personalizzati o programmabili per eseguire attività in modo più efficiente rispetto alle CPU generiche. Ciò sta accadendo per due ragioni. Il primo è che quando alcune attività maturano, diventa più efficiente eseguire le attività tramite hardware dedicato piuttosto che tramite software. Anche se alcune di queste attività possono ancora essere eseguite utilizzando un motore di elaborazione programmabile, esistono molti motori programmabili come DSP, GPU, NPU e FPGA che potrebbero essere in grado di eseguire determinate attività in modo più efficiente rispetto alle CPU a causa della natura del carico di lavoro e/o la progettazione dei nuclei di lavorazione.

La seconda ragione per l’aumento degli acceleratori è il rallentamento della legge di Moore. Poiché diventa difficile migliorare le prestazioni e l’efficienza della CPU attraverso la tecnologia di produzione dei semiconduttori, l’industria si sta spostando maggiormente verso miglioramenti dell’architettura eterogenea. Progettando core di elaborazione più efficienti, che siano dedicati a una funzione specifica o ottimizzati attorno a un tipo specifico di carico di lavoro o esecuzione, è possibile ottenere prestazioni ed efficienza significativamente migliorate nello stesso spazio o in una quantità simile. Di conseguenza, la direzione da seguire è l’elaborazione accelerata. Anche le tecnologie innovative come l’informatica quantistica e neuromorfa, due aree in cui la ricerca IBM sta guidando il settore, sono davvero forme di elaborazione accelerata che miglioreranno le piattaforme di elaborazione tradizionali.

L’intelligenza artificiale è uno dei carichi di lavoro più comuni in fase di accelerazione e vi è un’ampia varietà di processori e acceleratori in fase di sviluppo sia per l’addestramento all’intelligenza artificiale che per l’elaborazione dell’inferenza. I vantaggi di ciascuno dipenderanno dall’efficienza con cui l’acceleratore elabora particolari carichi di lavoro. Per i server, la maggior parte degli acceleratori di intelligenza artificiale sono chip discreti. Sebbene questo offra più area di silicio per prestazioni di picco più elevate, aumenta anche i costi, il consumo energetico, la latenza e la variabilità nell’esecuzione delle attività di intelligenza artificiale. L’approccio di IBM di aggiungere l’acceleratore AI sul chip e interfacciarlo direttamente con i core della CPU e condividere la memoria consentirà un’elaborazione sicura in tempo reale o quasi in tempo reale dei modelli AI, aumentando l’efficienza complessiva del sistema. E poiché il processore è destinato a carichi di lavoro di classe enterprise, a differenza dei grandi carichi di lavoro di ricerca come la modellazione scientifica o finanziaria, è probabile che le richieste siano distribuite su più modelli di intelligenza artificiale con requisiti a bassa latenza. Gli acceleratori di intelligenza artificiale sono stati progettati per carichi di lavoro aziendali come il rilevamento delle frodi, nonché per la gestione del sistema e dell’infrastruttura come il posizionamento del carico di lavoro, i piani di query del database e il rilevamento delle anomalie.

L’acceleratore AI presenta un array di matrici con 128 riquadri di elaborazione progettati per operazioni SIMD FP-16 a 8 vie e un array di attivazione con trentadue riquadri progettati per operazioni SIMD FP-16/FP-32 a 8 vie. Il motivo per i due array è dividere le operazioni tra funzioni di moltiplicazione e convoluzione di matrici più semplici e funzioni più complesse come sigmoid o softmax ottimizzando l’esecuzione di ciascuna. I due array sono collegati tramite un Intelligent Data Mover e Formatter capace di 600 GB/s di larghezza di banda internamente e dispongono di prefetcher programmabili e motori di write-back collegati alle cache su chip con più di 120 GB/s di larghezza di banda. Secondo IBM, il processore AI esegue il multiplexing dei carichi di lavoro AI dalle varie CPU e ha prestazioni aggregate di oltre 6 TFLOPS per chip e si prevede che siano oltre 200 TLFOPS per un rack completamente popolato. L’acceleratore AI utilizza anche gli strumenti AI progettati per funzionare con altre piattaforme IBM da IBM Deep Learning Compiler per il porting e l’ottimizzazione dei modelli addestrati sulla piattaforma e sulle librerie di modelli Snap ML.

Secondo IBM, la nuova struttura della cache ha comportato un aumento delle prestazioni stimato del 40% nelle prestazioni per socket. Ciò è impressionante data una piattaforma che si è evoluta in un mainframe scalabile ottimizzato in tutto lo stack e fino al processore. Ironia della sorte, proprio come una volta la legge di Moore ha allontanato il settore da processori e sistemi personalizzati, ora riporta il settore alla personalizzazione nell’era dell’informatica accelerata. Sebbene i ricavi di IBM siano guidati da software e servizi, l’esperienza che guida tutto, dalla produzione di semiconduttori a chip e sistemi personalizzati, offre a IBM un vantaggio competitivo in questo nuovo mondo accelerato incentrato sull’ottimizzazione del carico di lavoro.